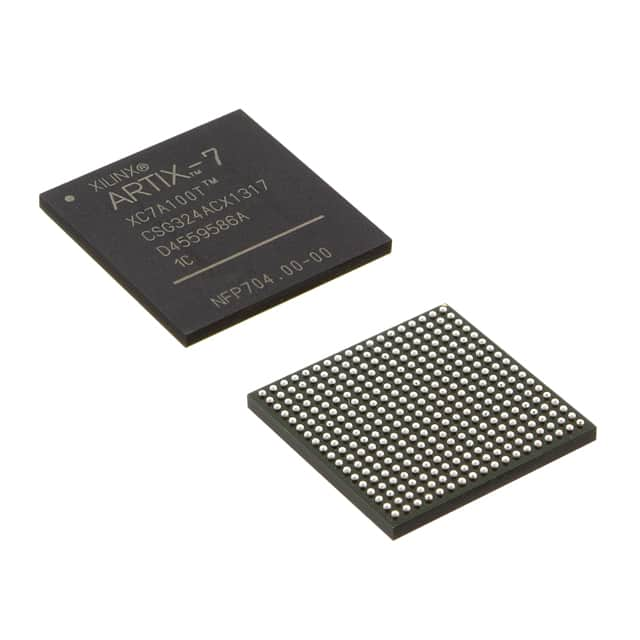

Orihinal na IC chip Programmable XCVU440-2FLGA2892I IC FPGA 1456 I/O 2892FCBGA

Mga katangian ng produkto

| URI | PAGLALARAWAN |

| Kategorya | Integrated Circuits (ICs) |

| Mfr | AMD Xilinx |

| Serye | Virtex® UltraScale™ |

|

| Kahon |

| Standardd Pakete | 1 |

| Katayuan ng Produkto | Aktibo |

| Bilang ng mga LAB/CLB | 316620 |

| Bilang ng Logic Elements/Cell | 5540850 |

| Kabuuang Mga Bit ng RAM | 90726400 |

| Bilang ng I/O | 1456 |

| Boltahe – Supply | 0.922V ~ 0.979V |

| Uri ng Pag-mount | Ibabaw na Mount |

| Operating Temperatura | -40°C ~ 100°C (TJ) |

| Package / Case | 2892-BBGA, FCBGA |

| Package ng Supplier ng Device | 2892-FCBGA (55×55) |

| Batayang Numero ng Produkto | XCVU440 |

Paggamit ng mga FPGA bilang mga tagaproseso ng trapiko para sa seguridad ng network

Ang trapiko papunta at mula sa mga security device (mga firewall) ay naka-encrypt sa maraming antas, at ang L2 encryption/decryption (MACSec) ay pinoproseso sa link layer (L2) na mga node ng network (mga switch at router).Karaniwang kinabibilangan ng mas malalim na pag-parse, L3 tunnel decryption (IPSec) ang pagpoproseso sa kabila ng L2 (MAC layer) at naka-encrypt na trapiko ng SSL na may trapikong TCP/UDP.Ang pagpoproseso ng packet ay kinabibilangan ng pag-parse at pag-uuri ng mga papasok na packet at ang pagproseso ng malalaking volume ng trapiko (1-20M) na may mataas na throughput (25-400Gb/s).

Dahil sa malaking bilang ng mga computing resources (cores) na kinakailangan, ang mga NPU ay maaaring gamitin para sa medyo mas mataas na bilis ng pagpoproseso ng packet, ngunit ang mababang latency, mataas na pagganap na scalable na pagpoproseso ng trapiko ay hindi posible dahil ang trapiko ay pinoproseso gamit ang MIPS/RISC core at pag-iskedyul ng mga naturang core. base sa kanilang availability ay mahirap.Ang paggamit ng mga kagamitang panseguridad na nakabatay sa FPGA ay maaaring epektibong maalis ang mga limitasyong ito ng mga arkitektura na nakabatay sa CPU at NPU.

Pagproseso ng seguridad sa antas ng aplikasyon sa mga FPGA

Ang mga FPGA ay mainam para sa inline na pagpoproseso ng seguridad sa mga susunod na henerasyong firewall dahil matagumpay nilang natutugunan ang pangangailangan para sa mas mataas na performance, flexibility, at low-latency na operasyon.Bilang karagdagan, ang mga FPGA ay maaari ding magpatupad ng mga pag-andar ng seguridad sa antas ng aplikasyon, na higit pang makakatipid sa mga mapagkukunan ng computing at mapahusay ang pagganap.

Kasama sa mga karaniwang halimbawa ng pagpoproseso ng seguridad ng aplikasyon sa mga FPGA

- TTCP offload engine

- Regular na pagtutugma ng expression

- Pagproseso ng Asymmetric encryption (PKI).

- Pagproseso ng TLS

Mga susunod na henerasyong teknolohiya ng seguridad gamit ang mga FPGA

Maraming umiiral na asymmetric na algorithm ang madaling makompromiso ng mga quantum computer.Ang mga asymmetric na algorithm ng seguridad gaya ng RSA-2K, RSA-4K, ECC-256, DH, at ECCDH ang pinaka-apektado ng mga diskarte sa quantum computing.Ang mga bagong pagpapatupad ng asymmetric algorithm at NIST standardization ay ginagalugad.

Kasama sa kasalukuyang mga panukala para sa post-quantum encryption ang Ring-on-Error Learning (R- LWE) na paraan para sa

- Public Key Cryptography (PKC)

- Mga digital na lagda

- Key paglikha

Kasama sa iminungkahing pagpapatupad ng public key cryptography ang ilang kilalang mathematical operations (TRNG, Gaussian noise sampler, polynomial addition, binary polynomial quantifier division, multiplication, atbp.).Ang FPGA IP para sa marami sa mga algorithm na ito ay magagamit o maaaring mahusay na maipatupad gamit ang mga bloke ng gusali ng FPGA, tulad ng mga DSP at AI engine (AIE) sa mga umiiral at susunod na henerasyong Xilinx device.

Inilalarawan ng puting papel na ito ang pagpapatupad ng L2-L7 na seguridad gamit ang isang programmable na arkitektura na maaaring i-deploy para sa pagpapabilis ng seguridad sa mga edge/access network at mga susunod na henerasyong firewall (NGFW) sa mga network ng enterprise.